Type of Adders with Verilog Code - các loại bộ cộng bằng Verilog

Saturday, 08 May 2021 19:58

Semicon Editor 01

Addition on 2 -bit ->

d_out[1:0] = a_in + b_in ;

Half Adder ->

Last Updated ( Saturday, 08 May 2021 20:03 )

Read more...

|

Clock Dividers and Multipliers - Bộ chia và nhân đồng hồ

Saturday, 08 May 2021 09:53

Semicon Editor 01

Q1 How to generate a divide by -N clock ?

Generate Divide by 2 Clock -

Below is circuit for Divide by 2 clock , this is nothing but a T-FlipFlop.

Last Updated ( Saturday, 08 May 2021 12:20 )

Read more...

Verilog Code for FIR Filter - Code Verilog cho bộ lọc FIR

FIR filters are is widely used in different applications such as biomedical, communication and control due to its easily implementation, stability and best performance. Its simplicity makes it attractive for many applications where it is need to minimize computational requirements.

Read more...

Verilog code for counting number of 1's and number of 0's in parallel data

Thursday, 06 May 2021 11:53

Semicon Editor 01

Here is the verilog code for counting number of 1's and number of 0's in parallel data. since data is continuously changing on every clock cycle, counting has to be done using parallel hardware.

Last Updated ( Thursday, 06 May 2021 12:06 )

Read more...

Asynchronous FIFO with Programmable Depth - FIFO Bất đồng bộ with Depth được lập trình

Thursday, 06 May 2021 11:41

Semicon Editor 01

Asynchronous FIFO Design Asynchronous FIFO Verilog Code Asynchronous FIFO with block diagram and verilog Code.

Last Updated ( Thursday, 06 May 2021 20:49 )

Read more...

Serial Peripheral Interface - SPI

Monday, 03 May 2021 21:35

Semicon Editor 01

Serial Peripheral Interface Bus

The Serial Peripheral Interface (SPI) bus is a synchronous serial communication interface specification used for short distance communication, primarily in embedded systems. The interface was developed by Motorola and has become a de facto standard. Typical applications include Secure Digital cards and liquid crystal displays.

Last Updated ( Monday, 03 May 2021 21:43 )

Read more...

Complex Number - Số Phức

Monday, 03 May 2021 21:32

Semicon Editor 01

A complex number is a number that can be expressed in the form a + bi, where a and b are real numbers and i is the imaginary unit, that satisfies the equation i2 = −1.[1] In this expression, a is the real part and b is the imaginary part of the complex number.

Last Updated ( Thursday, 06 May 2021 20:48 )

Read more...

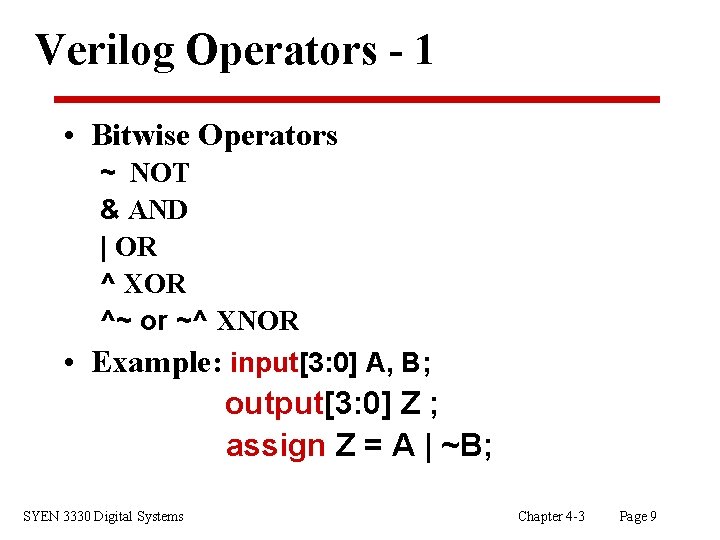

Verilog Operators - Toán tử trong Verilog

Monday, 03 May 2021 21:23

Semicon Editor 01

Verilog HDL operators are same as in C language. Verilog HDL operators are same as in C language.

{} - concatenation

usage -

Last Updated ( Thursday, 06 May 2021 20:50 )

Read more...

Convergence , divergence and re-convergence

Sunday, 02 May 2021 19:59

Semicon Editor 01

Now a days , multiple clocks in a system are common due to increasing frequency and complexity. A CDC check is a must check on the design before tapping out as any CDC violation may be fatal and could be a cause of chip failure.

Last Updated ( Sunday, 02 May 2021 20:03 )

Read more...

Verilog Code for 8-bit ALU - Code Verilog cho 8-bit ALU

Sunday, 02 May 2021 19:00

Semicon Editor 01

/*

*inst[3:0] = 4'h0 => reserved

*inst[3:0] = 4'h1 => Addition

*inst[3:0] = 4'h2 => Substraction

Last Updated ( Thursday, 06 May 2021 20:51 )

Read more...

What is MTBF ? - MTBF là gì?

Friday, 30 April 2021 23:53

Semicon Editor 01

Few terms- Set-Up Time The time required for the input data signal at a flip flop to be valid before the incoming clock edge arrives. Hold Time The time required for the input data signal to remain valid after the clock edge as transitioned.

Last Updated ( Thursday, 06 May 2021 20:53 )

Read more...

Reset Removal and Recovery time

Friday, 30 April 2021 23:43

Semicon Editor 01

These are timing checks for asynchronous signals similar to the setup and hold checks. These are timing checks for asynchronous signals similar to the setup and hold checks.

Recovery time is the minimum amount of time required between the release of an asynchronous signal from the active state to the next active clock edge.

Last Updated ( Friday, 30 April 2021 23:49 )

Read more...

Low Power Design and Verification

Friday, 30 April 2021 23:36

Semicon Editor 01

Low power design is not a new area, but it was not that much important as it is now. Semiconductor market trend is very fast changing , and it is a challenge to face and ready with new technology.

Last Updated ( Wednesday, 05 May 2021 13:53 )

Read more...

Difference between PLL and DLL

Thursday, 29 April 2021 13:51

Semicon Editor 01

In electronics, a delay-locked loop (DLL) is a digital circuit similar to a phase-locked loop (PLL), with the main difference being the absence of an internal voltage-controlled oscillator, replaced by a delay line. In electronics, a delay-locked loop (DLL) is a digital circuit similar to a phase-locked loop (PLL), with the main difference being the absence of an internal voltage-controlled oscillator, replaced by a delay line.

Last Updated ( Thursday, 29 April 2021 13:55 )

Read more...

Digital PPL

Thursday, 29 April 2021 13:46

Semicon Editor 01

A phase-locked loop or phase lock loop (PLL) is a control system that generates an output signal whose phase is related to the phase of an input signal. A phase-locked loop or phase lock loop (PLL) is a control system that generates an output signal whose phase is related to the phase of an input signal.

VCO -> Voltage Controlled Oscillator

Last Updated ( Thursday, 29 April 2021 13:48 )

Read more...

The future of semiconductor

Thursday, 29 April 2021 13:16

Semicon Editor 01

Everyone in semiconductor industry is wondering ,where semiconductor industry will go in next 5 years or so .. what are the career opportunities and scope in future at fresher level as well as experience level ? Everyone in semiconductor industry is wondering ,where semiconductor industry will go in next 5 years or so .. what are the career opportunities and scope in future at fresher level as well as experience level ?

Last Updated ( Thursday, 29 April 2021 13:27 )

Read more...

|

|

|

|

|

|

|

Page 23 of 118 |

Addition on 2 -bit ->

Addition on 2 -bit ->

Addition on 2 -bit ->

Addition on 2 -bit ->