HOW TO BUILD UVM ENVIRONMENT PART – 1

Wednesday, 02 June 2021 21:06

Semicon Editor 01

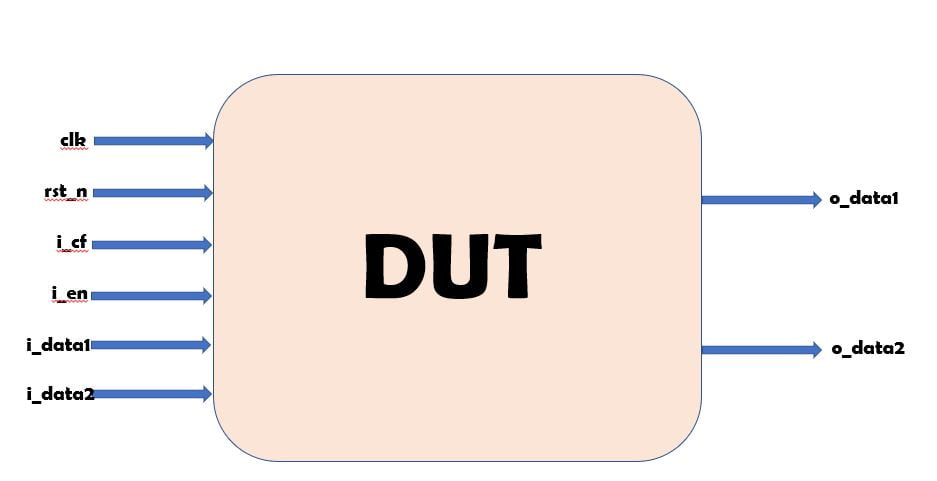

We learned which all components are required to develop UVM Environment/Testbench to verify complex Designs. In this blog post we will verify a small RTL Design by developing complete UVM Environment.

Last Updated ( Wednesday, 02 June 2021 21:08 )

Read more...

|

UVM TLM CONCEPTS

Saturday, 29 May 2021 14:09

Semicon Editor 01

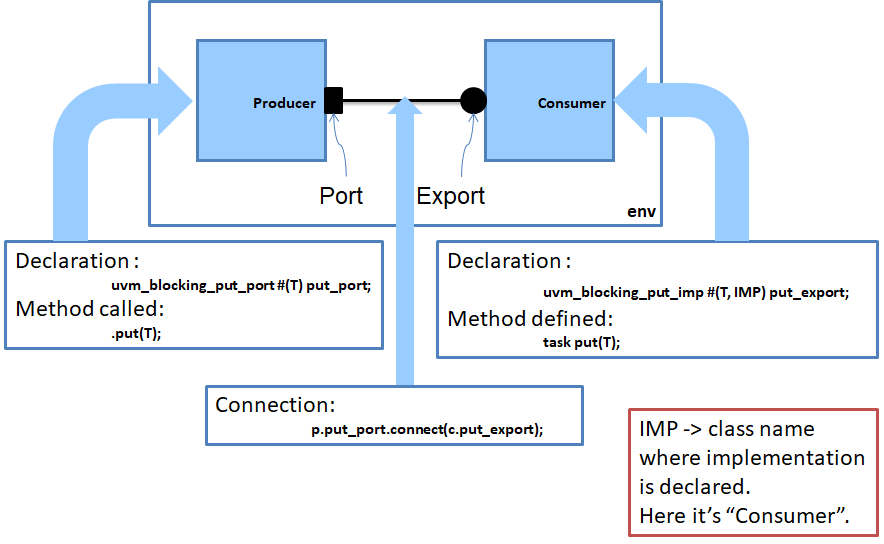

It is necessary to manage most of the verification tasks, such as generating stimulus and collecting coverage data, at the transaction level, which is the natural way of verification engineers tend to think of the activity of a system.

Last Updated ( Saturday, 29 May 2021 14:11 )

Read more...

ENCAPSULATION

Saturday, 29 May 2021 14:01

Semicon Editor 01

Many times we might use the Base Class or Base Class library provided by third party sources. By default, These Class Members are Public in nature.

Last Updated ( Saturday, 29 May 2021 14:04 )

Read more...

MAILBOX IN SYSTEM VERILOG

Thursday, 27 May 2021 12:42

Semicon Editor 01

While learning System Verilog you always thought like How do you pass information between two threads/processes?

Last Updated ( Thursday, 27 May 2021 12:49 )

Read more...

POLYMORPHISM

Thursday, 27 May 2021 12:39

Semicon Editor 01

Polymorphism is the ability to have the same code act differently based on the type of the Object that its being working with. This is a key topic of any Object Oriented Programming language. SystemVerilog enables

Last Updated ( Thursday, 27 May 2021 12:41 )

Read more...

“STATIC PROPERTIES AND STATIC METHODS” - Các thuộc tính và phương thức "static" trong SystemVerilog

Thursday, 27 May 2021 12:34

Semicon Editor 01

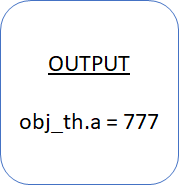

STATIC Properties: As we know that in SystemVerilog Class Properties do not get created until the Object gets constructed. But there is an exception to that. When we add a “static”

Last Updated ( Saturday, 29 May 2021 13:54 )

Read more...

LOGIC IN SYSTEMVERILOG

Tuesday, 25 May 2021 14:41

Semicon Editor 01

Before we start understanding the “logic” data type for system Verilog, Let’s refresh verilog data types “reg” and “wire”. Before we start understanding the “logic” data type for system Verilog, Let’s refresh verilog data types “reg” and “wire”.

Last Updated ( Tuesday, 25 May 2021 14:44 )

Read more...

CONCEPT OF “THIS” IN SYSTEM VERILOG - Ý nghĩa của "This" trong Systemverilog

Sunday, 23 May 2021 14:47

Semicon Editor 01

Concept and usage of “this” is simple but important in test bench development using system verilog. I would like to share some insights on this concept.

Last Updated ( Tuesday, 25 May 2021 16:12 )

Read more...

SHALLOW COPY VS DEEP COPY

Sunday, 23 May 2021 14:43

Semicon Editor 01

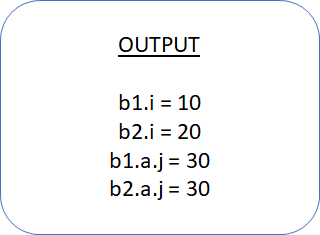

Shallow Copy: As we know that Classes contains Properties and Methods. A Class may also contain other Class Instantiation as a part of it. All these variables inside a Class got initialized once the Class is constructed.

Last Updated ( Sunday, 23 May 2021 14:46 )

Read more...

HOW UVM PHASING IS TRIGGERED ? - PHASING UVM ĐƯỢC ĐIỀU CHỈNH NHƯ THẾ NÀO ?

Saturday, 22 May 2021 14:55

Semicon Editor 01

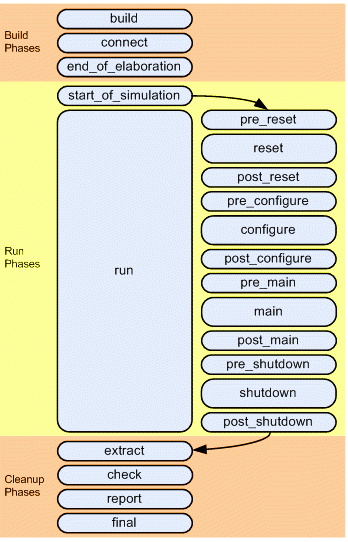

To start a UVM Testbench, the run_test() method has to be called from the static part of the Testbench i.e called from an initial block in the top module of the Testbench.

Last Updated ( Saturday, 22 May 2021 15:00 )

Read more...

UVM PHASING

Saturday, 22 May 2021 14:52

Semicon Editor 01

Today I’m going to share something which is so common to almost every concept of UVM. In other way, we can say that this concept is the backbone of the UVM Verification Methodology. This is related to the process which deals from the starting of the simulation till end of the simulation.

Last Updated ( Saturday, 22 May 2021 14:54 )

Read more...

FUNCTIONAL COVERAGE OPTIONS IN SYSTEM VERILOG - Functional coverage trong System Verilog

Wednesday, 19 May 2021 23:27

Semicon Editor 01

Functional Coverage is very important in Test Bench Development. It always gives us a confidence on covered items listed on verification plan.

Last Updated ( Thursday, 20 May 2021 14:20 )

Read more...

COVERAGE

Wednesday, 19 May 2021 23:21

Semicon Editor 01

Coverage is used as a metric for evaluating the progress of a verification project. Coverage metric forms an important part of measuring progress in constrained random testbenches and also provides good feedback to the quality and effectiveness of constrained random testbenches.

Last Updated ( Wednesday, 19 May 2021 23:24 )

Read more...

GENERAL QUESTIONS ON COVERAGE - Những câu hỏi tổng quan về Coverage

Wednesday, 19 May 2021 23:17

Semicon Editor 01

1. What is the difference between code coverage and functional coverage? There are two types of coverage metrics commonly used in Functional Verification to measure the completeness and efficiency of verification process.

Last Updated ( Thursday, 20 May 2021 14:21 )

Read more...

UVM_REPORT_CATCHER/UVM_ERROR DEMOTER EXAMPLE - ví dụ về UVM_REPORT_CATCHER/UVM_ERROR DEMOTER

Monday, 17 May 2021 22:21

Semicon Editor 01

Sometimes user will face a situation where you need some of the components from environment to demote error message means user want to disable error from a specific component.

Last Updated ( Tuesday, 18 May 2021 11:30 )

Read more...

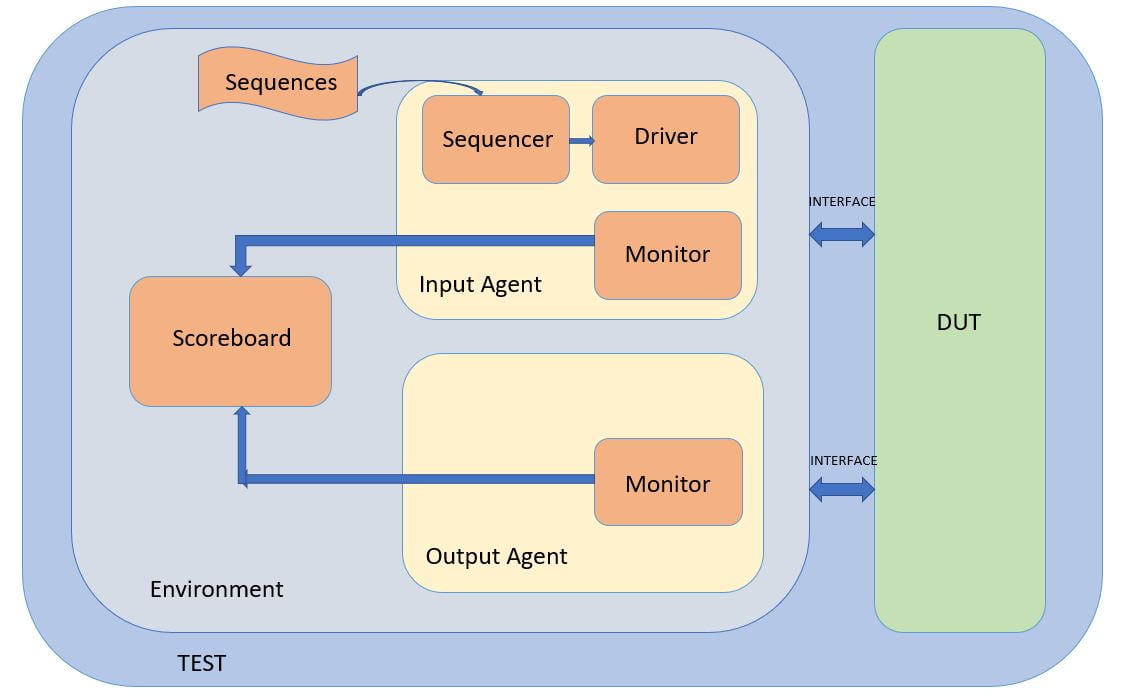

TYPICAL UVM TESTBENCH ARCHITECTURE - kiến trúc UVM TESTBENCH điển hình

Monday, 17 May 2021 22:13

Semicon Editor 01

A typical UVM testbench contains several components. First, let’s look at a simple UVM testbench diagram.

Last Updated ( Tuesday, 18 May 2021 11:31 )

Read more...

|

|

|

|

|

|

|

Page 21 of 118 |