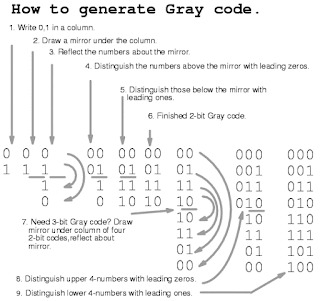

How to do binary to gray code conversion -

How to do binary to gray code conversion -

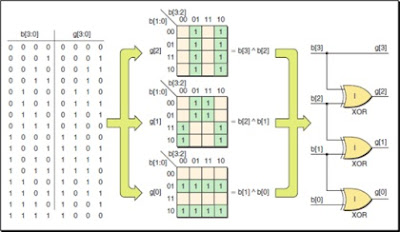

Verilog Code for Binary to Gray code conversion ->

Equation for Gray code

Hardware for Binary to Gray Code ->

/*Logic to convert binary numbers into Gray coded binary numbers is implemented in the following Verilog Code.

*/

module binary2gray();

reg clk;

reg rstn;

reg [5:0] counter_binary, counter_binary_reg, counter_gray, counter_gray_reg;

integer count, file_wr;

/* Initial block to generate clock and reset */

initial begin

clk = 0; rstn = 0; #100 rstn = 1;

forever begin

#10 clk = !clk;

end end

/* Synchronous Logic for registering the data and incrementing the counter for binary data */

always @ (posedge clk or negedge rstn)

begin

if (!rstn) begin

counter_binary_reg <= 'b0;

counter_gray_reg <= 'b0; end

else begin

counter_binary_reg <= counter_binary + 1;

counter_gray_reg <= counter_gray;

$display("binary number= 6'b%b : gray en-coded binary number = 6'b%b", counter_binary_reg, counter_gray_reg); end end

/* Logic is to get Gray code from Binary code */

function[5:0] binary2gray ;

input[5:0] value;

integer i;

begin

binary2gray[5] = value[5];

for (i=5; i>0; i = i - 1)

binary2gray[i-1] = value[i] ^ value[i - 1];

end

endfunction

/* Get gray encoded output */

always @(*)

begin

counter_gray = counter_gray_reg;

counter_binary = counter_binary_reg;

counter_gray = binary2gray(counter_binary_reg); end

endmodule

Bạn Có Đam Mê Với Vi Mạch hay Nhúng - Bạn Muốn Trau Dồi Thêm Kĩ Năng

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn