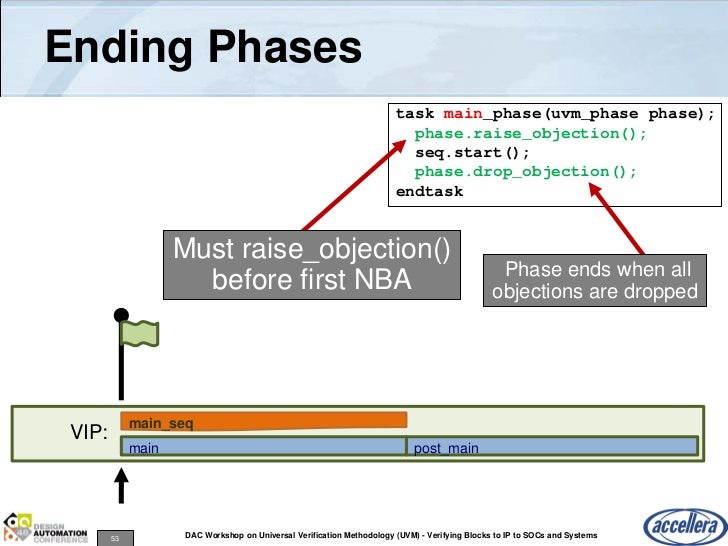

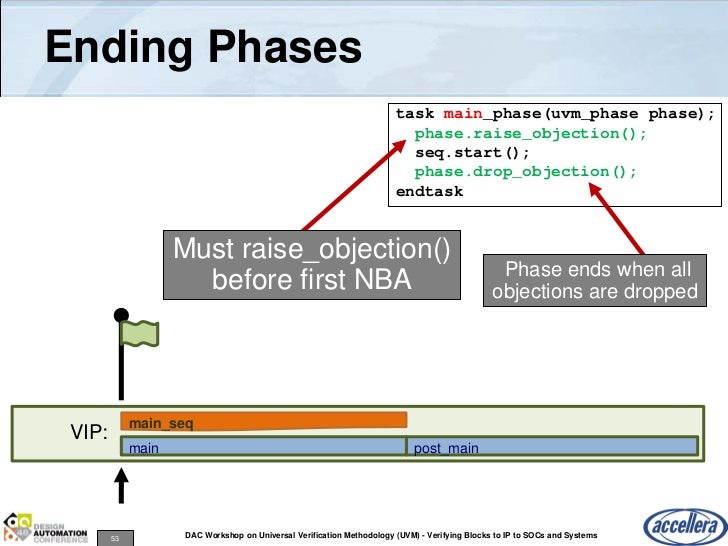

RAISE/DROP OBJECTION AUTOMATICALLY WITH UVM

Tuesday, 15 June 2021 15:01

Semicon Editor 01

Variable uvm_sequence_base::starting_phase is deprecated and replaced by two new methods set_starting_phase and get_starting_phase, which prevent starting_phase from being modified in the middle of a phase. This change is not backward-compatible with UVM 1.1,

Read more...

|

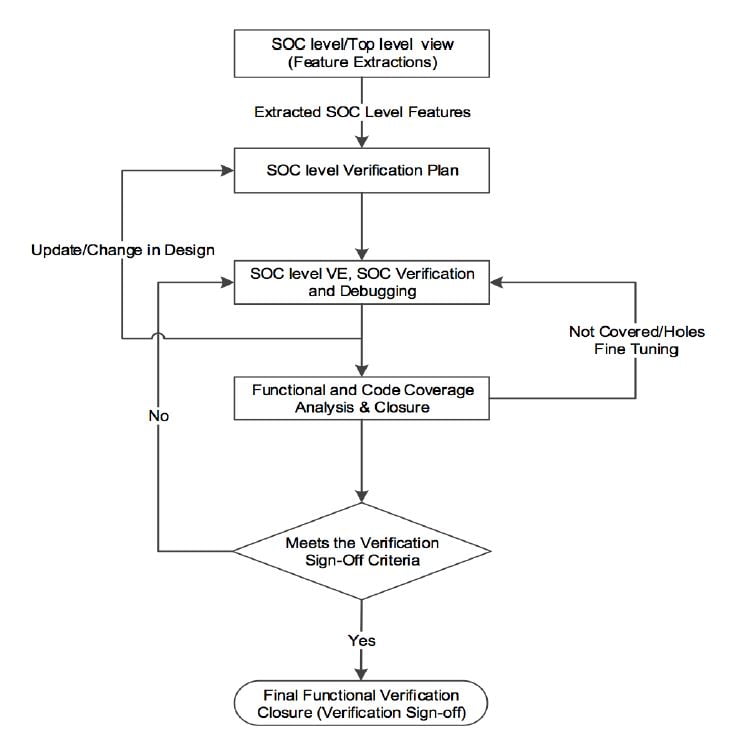

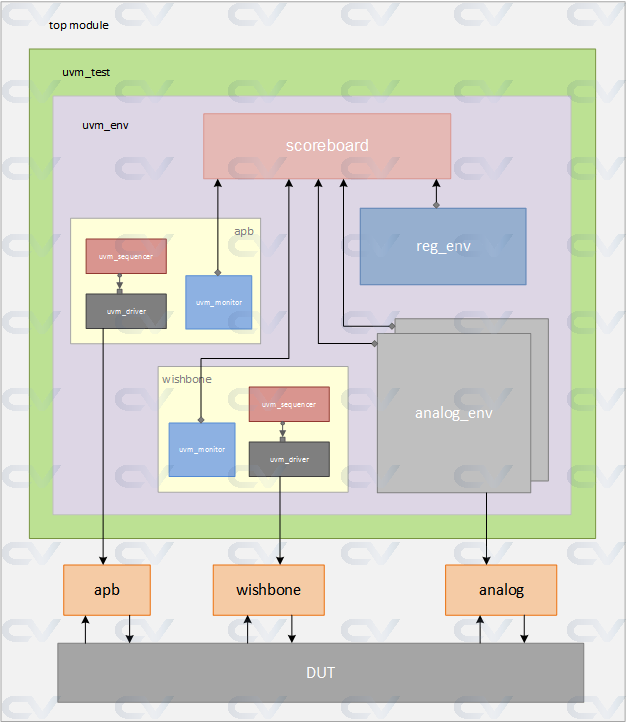

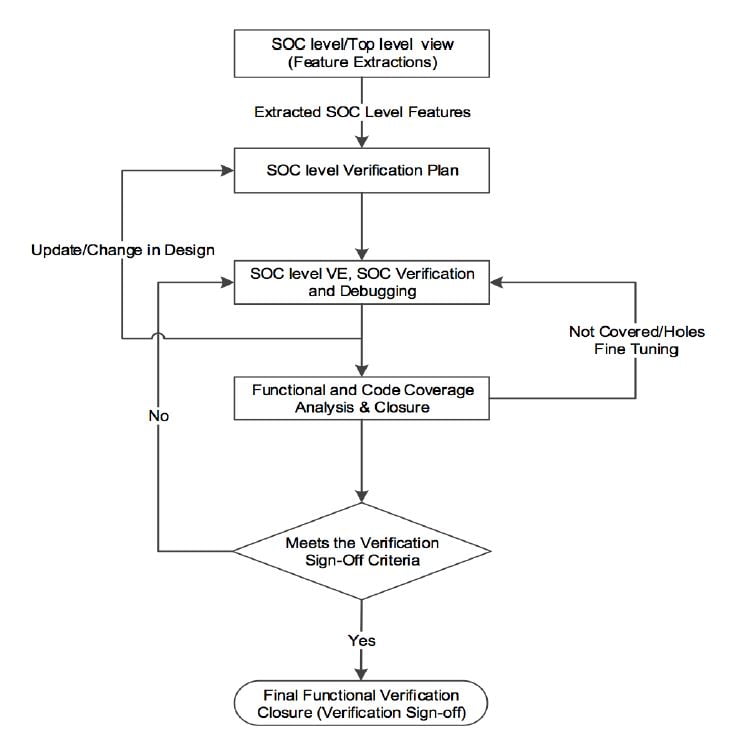

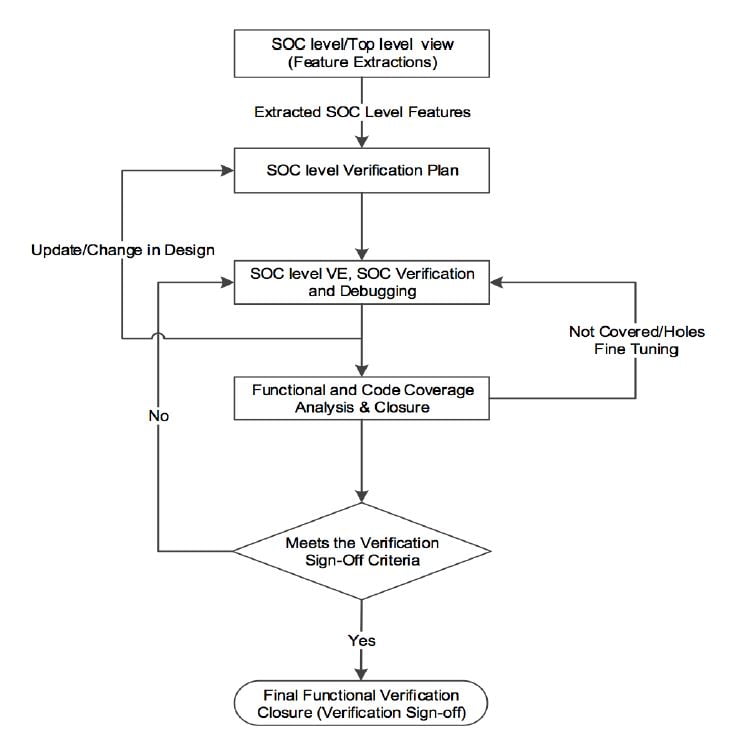

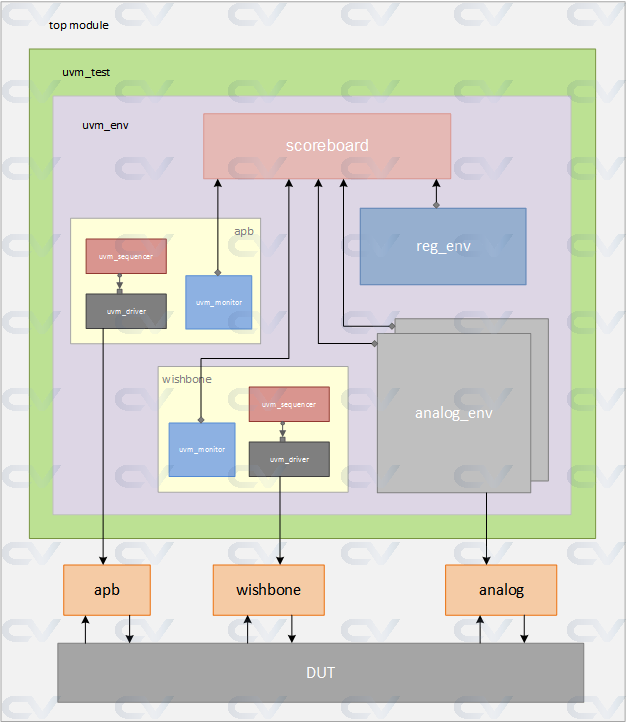

SOC VERIFICATION FLOW

Sunday, 13 June 2021 12:58

Semicon Editor 01

Many people do not appreciate what makes a system-on-chip (SoC) different from other semiconductor devices. Many companies, especially in electronic design automation (EDA), toss around the term “SoC” without defining it or explaining why it’s such an important concept.

Read more...

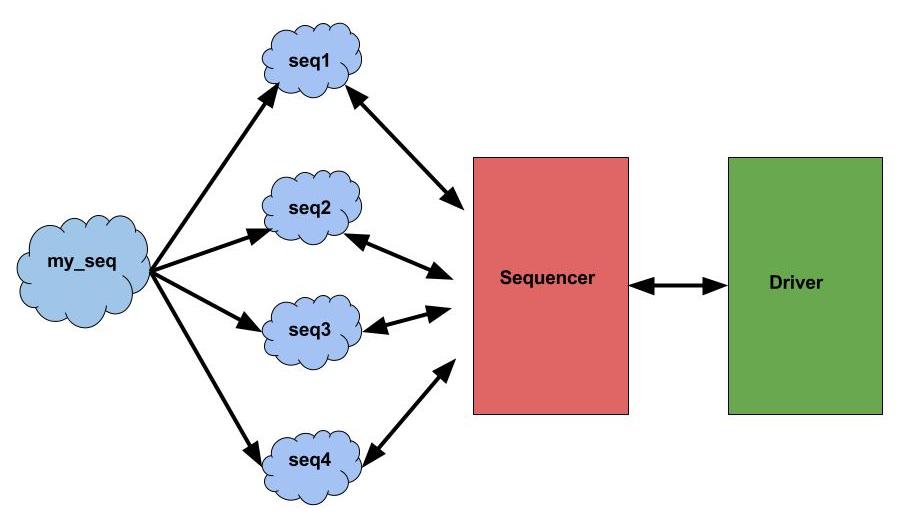

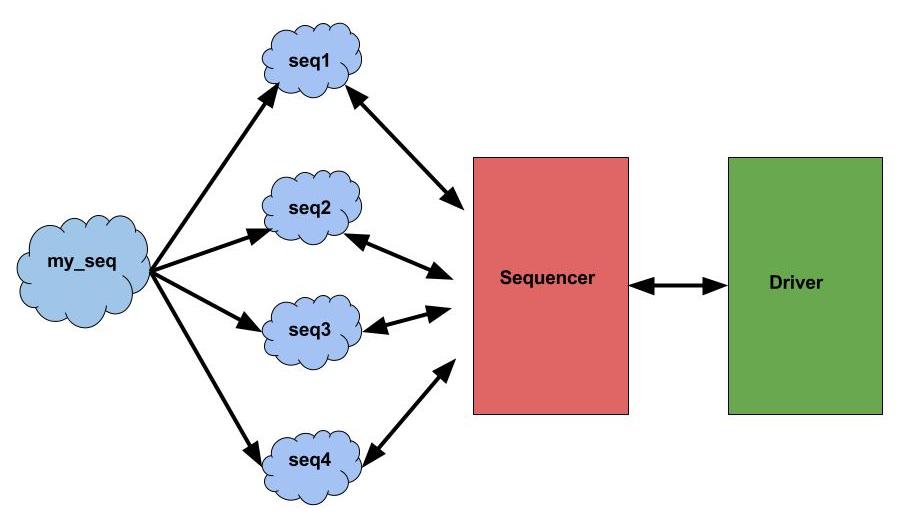

UVM SEQUENCE ARBITRATION MECHANISM

Sunday, 13 June 2021 12:54

Semicon Editor 01

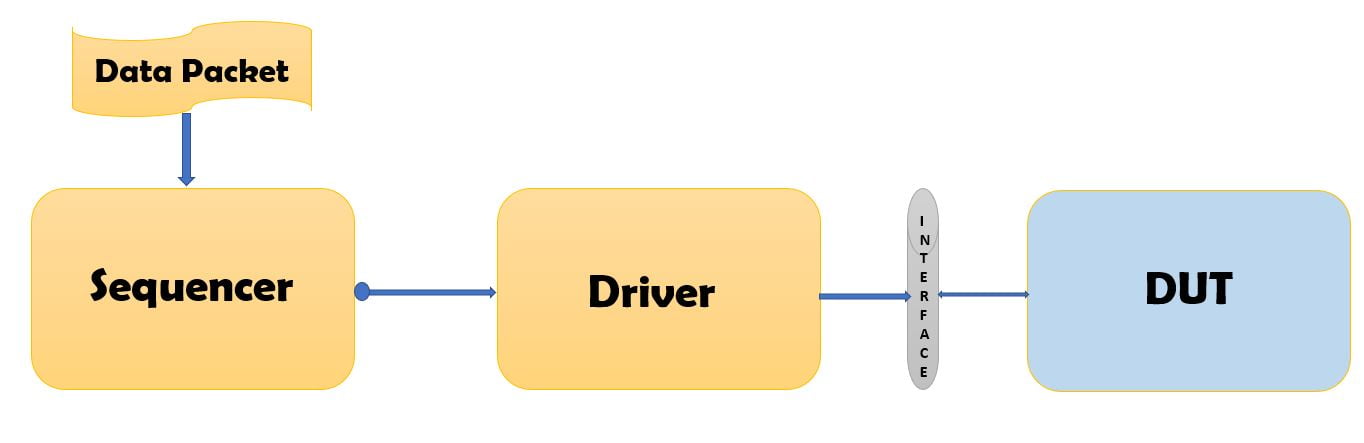

Multiple sequences can interact concurrently with a driver connected to a single interface. The sequencer supports an arbitration mechanism to ensure that at any point of time only one sequence has access to the driver. The choice of which sequence can send a sequence_item is dependent on a user selectable sequencer arbitration algorithm.

Read more...

HOW UVM CALLBACK WORKS?

Sunday, 13 June 2021 12:41

Semicon Editor 01

Callback mechanism is used for altering the behavior of the transactor/BFM without modifying the existing BFM/transactor. Callback gives flexibility to plug-and-play and reuse the components i.e. driver, monitor etc..

Last Updated ( Sunday, 13 June 2021 12:46 )

Read more...

SEMAPHORE IN SYSTEMVERILOG

Saturday, 12 June 2021 19:11

Semicon Editor 01

A semaphore allows you to control access to a resource.Conceptually, a semaphore is a bucket. When a semaphore is allocated, a bucket that contains a fixed number of keys is created.

Last Updated ( Saturday, 12 June 2021 19:20 )

Read more...

FLAVOURS OF FORK..JOIN

Wednesday, 09 June 2021 22:18

Semicon Editor 01

Fork…Join construct of System Verilog actually enables concurrent execution of each of its statements/threads/processes. This feature is most widely used for forking parallel processes/threads in System Verilog Test Benches.

Last Updated ( Wednesday, 09 June 2021 22:24 )

Read more...

UVM MACROS, MESSAGING AND UVM REPORTING

Wednesday, 09 June 2021 22:07

Semicon Editor 01

The UVM Library has built-in utility and field automation macros that allow objects to be created by the factory and have access to common functions such as copy( ) or clone( ).

Last Updated ( Wednesday, 09 June 2021 22:15 )

Read more...

PLUSARGS IN SYSTEMVERILOG

Tuesday, 08 June 2021 18:22

Semicon Editor 01

Plus args are command line switches supported by the simulator. Usually they are application specific. As per SystemVerilog LRM arguments beginning with the ‘+’ character will be available using the $test$plusargs and $value$plusargs PLI APIs.

Last Updated ( Wednesday, 09 June 2021 22:17 )

Read more...

VIRTUAL SEQUENCE AND SEQUENCERS

Sunday, 06 June 2021 00:21

Semicon Editor 01

Today I am going to talk about virtual sequences and the virtual sequencer. Common questions I hear from users include: why do we need a virtual sequence? How can we use it effectively?

Last Updated ( Sunday, 06 June 2021 00:27 )

Read more...

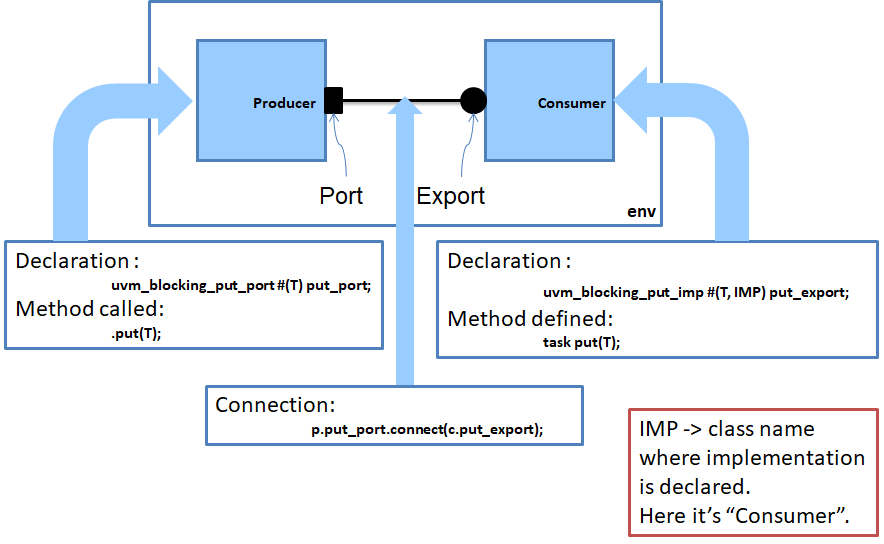

UVM TLM CONCEPTS

Sunday, 06 June 2021 00:18

Semicon Editor 01

It is necessary to manage most of the verification tasks, such as generating stimulus and collecting coverage data, at the transaction level, which is the natural way of verification engineers tend to think of the activity of a system.

Last Updated ( Sunday, 06 June 2021 00:20 )

Read more...

SOC VERIFICATION FLOW

Sunday, 06 June 2021 00:14

Semicon Editor 01

Many people do not appreciate what makes a system-on-chip (SoC) different from other semiconductor devices. Many companies, especially in electronic design automation (EDA), toss around the term “SoC” without defining it or explaining why it’s such an important concept.

Last Updated ( Sunday, 06 June 2021 00:16 )

Read more...

BASIC ASSERTIONS EXAMPLES PART-2

Wednesday, 02 June 2021 21:34

Semicon Editor 01

I hope you started understanding assertions and their operators well with practical examples. Let’s start learning more operators in this post.

Last Updated ( Wednesday, 02 June 2021 21:36 )

Read more...

BASIC ASSERTIONS EXAMPLES PART-1

Wednesday, 02 June 2021 21:25

Semicon Editor 01

System Verilog assertions always help to speed up the verification process and it’s very powerful and widely used in the ASIC verification. Identifying the right set of checkers in the verification plan and implementing them using effective SV assertions helps to quickly catch the design bugs and ultimately helps in high-quality design.

Last Updated ( Wednesday, 02 June 2021 21:33 )

Read more...

HOW TO BUILD UVM ENVIRONMENT PART – 4

Wednesday, 02 June 2021 21:15

Semicon Editor 01

The basic function of the scoreboard is to check the correctness of the output data of the design under test. The scoreboard you create should derive from uvm_scoreboard; however, there is no current functionality of the uvm_scoreboard.

Read more...

HOW TO BUILD UVM ENVIRONMENT PART – 3

Wednesday, 02 June 2021 21:12

Semicon Editor 01

As mentioned, an agent is a container that instantiates the driver, monitor, and sequencer. Agents can be either active or passive. In active mode, all three components are created, while in passive mode only the monitor is created. Since we have already built the necessary components, creating the agent is simply a matter of instantiating them.

Last Updated ( Wednesday, 02 June 2021 21:15 )

Read more...

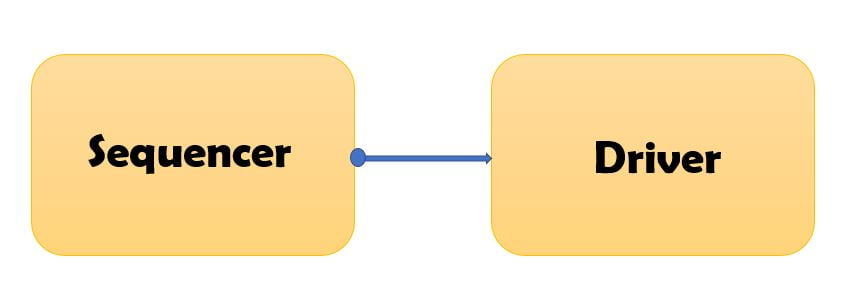

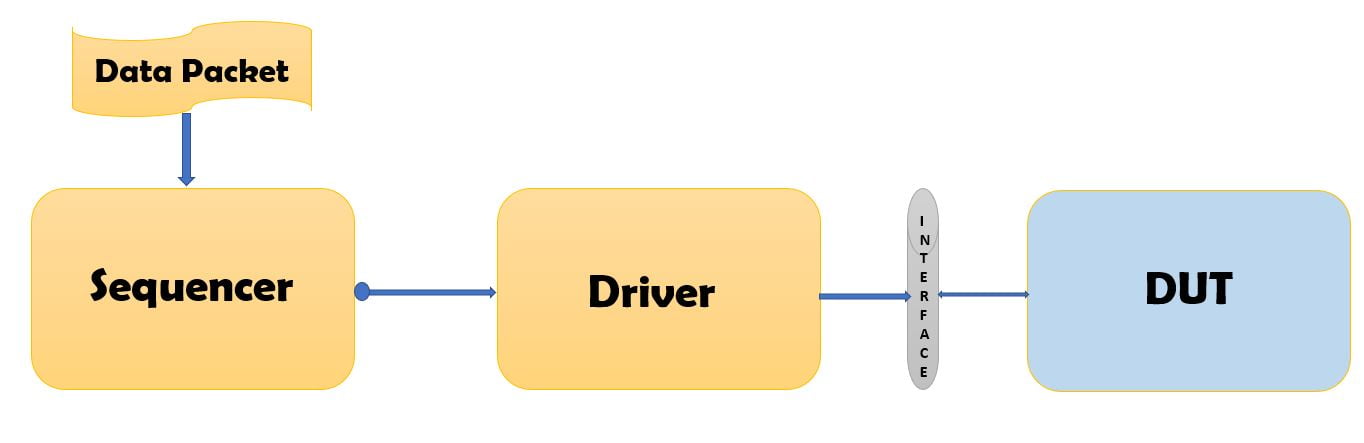

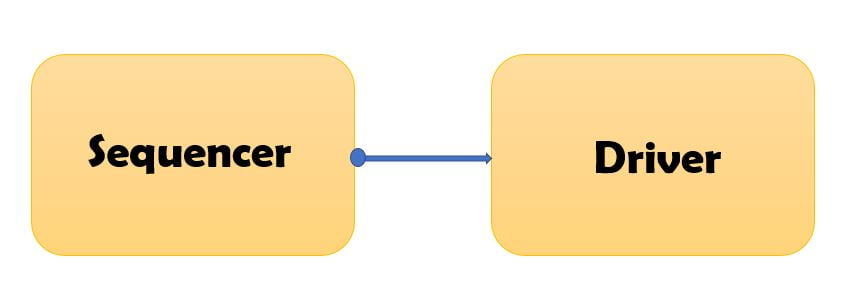

HOW TO BUILD UVM ENVIRONMENT PART – 2

Wednesday, 02 June 2021 21:08

Semicon Editor 01

The job of the sequencer is to control the flow of sequences to the driver. The fact that you can write six lines of code yet have a powerful implementation is the beauty of UVM. Having the sequencer mechanism prepared for you in the library allows you to build the testbench faster and more effectively.

Last Updated ( Wednesday, 02 June 2021 21:11 )

Read more...

|

|

|

|

|

|

|

Page 20 of 118 |