Verilog assertion có nhiều điểm hạn chế do bản thân ngôn ngữ không hỗ trợ trực tiếp việc viết Assertion mà phải thông qua các thư viện OVL hoặc PSL.

Verilog assertion có nhiều điểm hạn chế do bản thân ngôn ngữ không hỗ trợ trực tiếp việc viết Assertion mà phải thông qua các thư viện OVL hoặc PSL.

Thêm vào đó, assertion trong Verilog phải được viết sao cho transparent với các công cụ thiết kế (không được tổng hợp).

SystemVerilog Assertion khắc phục được các nhược điểm trên và hỗ trợ việc viết assertion một cách dễ dàng. Ưu điểm của SVA có thể kể đến như:

– Hỗ trợ viết assertion một cách ngắn gọn và súc tích.

– SVA mặc định sẽ không được tổng hợp bằng synthesis tool. Các kĩ sư thiết kế không phải tốn công thêm các pragma để tắt và mở assertion phục vụ cho synthesis

– SVA có thể được điều khiển để tắt mở như mong muốn, kể cả trong quá trình hệ thống đang reset.

– Hỗ trợ các severities khác nhau (mức độ cảnh báo lỗi)

SystemVerilog hỗ trợ hai cách viết assertion là immediate assertion và concurrent assertion

immediate assertion: Kiểm tra điều kiện tại một thời điểm xác định (thời điểm hiện tại)

syntax: tên_assertion(1) assert(2) điều_kiện_kiểm_tra(3) pass_state(4) else(5) failed_state(6)

(1): Tên assertion

(2): từ khóa

(3): Điều kiện kiểm tra của assertion

(4): Điều kiện thực thi nếu (3) pass

(5): từ khóa

(6): Điều kiện thực thi nếu (3) fail

Ví dụ về immediate assertion:

assert (data==read_data) $display (“Result is passed”); else $error(“Result is Failed”);

concurrent assertion: Kiểm tra điều kiện theo kiểu sequence (theo thời gian)

syntax: tên_assertion(1) assert property(2) điều_kiện_kiểm_tra(3) pass_state(4) else(5) failed_state(6)

Ví dụ về concurrent assertion

FULL_EMPTY assert property ( @(posedge clk) (!(buf_full &&buf_empty)) ) $display (“Result is passed”); else $error(“Result is Failed”);

Cho cả hai loại assertion, pass_state và failed_state là tùy chọn. Mặc định, nếu không khai báo:

– Nếu assertion pass, pass_state sẽ được bỏ qua

– Nếu assertion failed, công cụ kiểm tra sẽ in ra lỗi (error)

SVA hỗ trợ các loại severities sau:

$fatal

$error

$warning

$info

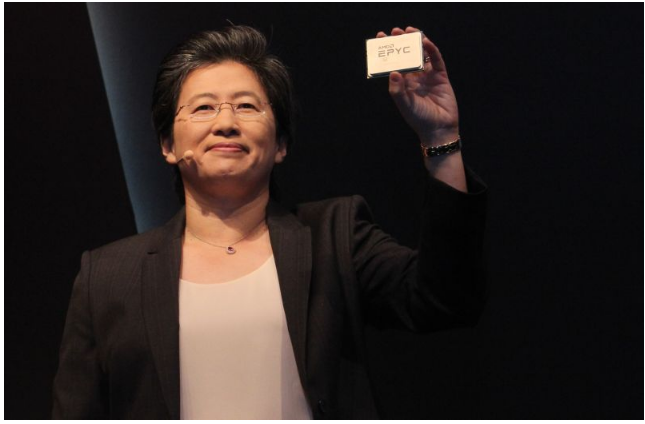

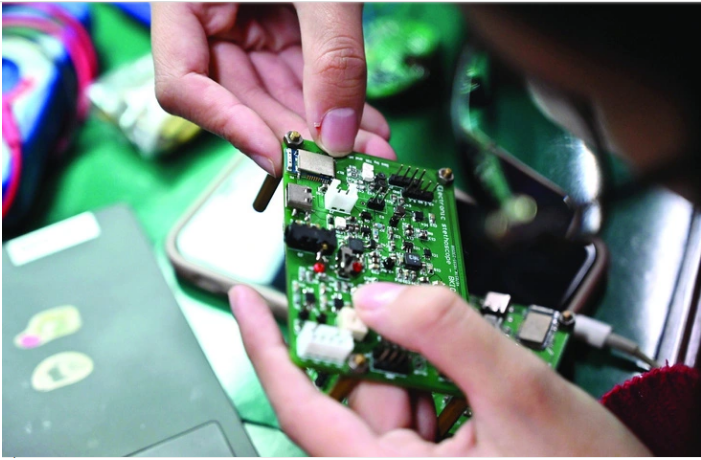

Bạn có đam mê ngành thiết kế vi mạch và bạn muốn có mức lương1000 usd

hãy đến với ngành vi mạch tại SEMICON