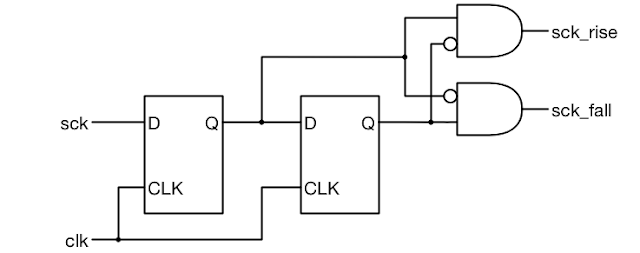

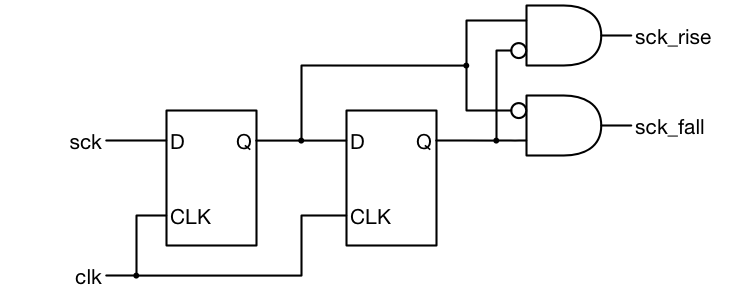

Circuit diagram for posedge detector and negedge detector :

Circuit diagram for posedge detector and negedge detector :

Below is the verilog code for positive detector and negative detector -

I have developed the testbench also , all in verilog :)

module pos_edge_detect ( clk, nrst, din, dout);

input clk;

input nrst;

input din;

output dout;

reg d_ff;

always @(posedge clk or negedge nrst) begin

if(!nrst)

d_ff <= 1'b0;

else

d_ff <= din;

end

// Positive edge detection

assign dout = din && (d_ff ^ din);

// Negative edge detection

// assign dout = (~din) && (d_ff ^ din);

endmodule

module tb1;

reg clk;

reg reset;

reg [4:0] count;

pos_edge_detect dut (.clk(clk),

.nrst(reset),

.din(count[0])

);

initial begin

clk = 0 ;

reset = 0;

count = 0 ;

end

always #5 clk <= ~clk;

initial begin

#100;

reset = 1;

end

always @(posedge clk)

count <= count + 3 + count[2] ;

initial begin

$dumpfile("temp.vcd");

$dumpvars();

#3000;

$finish;

end

endmodule

Bạn Có Đam Mê Với Vi Mạch hay Nhúng - Bạn Muốn Trau Dồi Thêm Kĩ Năng

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn