1. Giới thiệu

Có nhiều ngôn ngữ có thể lập trình cho FPGA như VHDL, Verilog, C… Mỗi ngôn ngữ lại có ưu nhược điểm riêng. Ví dụ như Verilog là ngôn ngữ được phát triển và sử dụng chủ yếu ở Mỹ. Đây là một ngôn ngữ rất gần với C, chính vì vậy sẽ rất thuận tiện cho ai đó đã quen lập trình với ngôn ngữ C. Tuy nhiên, ở châu Âu thì người ta lại quen dùng VHDL hơn. Ưu điểm của ngôn ngữ này là người làm việc với nó sẽ có cái nhìn rất thấu đáo về phần cứng.

2. Ngôn ngữ VHDL

2.1. Khái niệm

VHDL là ngôn ngữ mô tả phần cứng cho các mạch tích hợp tốc độ rất cao, là một loại ngôn ngữ mô tả phần cứng được phát triển dùng cho chương trình VHSIC (Very High Speed Itergrated Circuit) của bộ quốc phòng Mỹ. Mục tiêu của việc phát triển VHDL là có được một ngôn ngữ mô phỏng phần cứng tiêu chuẩn và thống nhất cho phép thử nghiệm các hệ thống số nhanh hơn cũng như cho phép dễ dàng đưa các hệ thống đó vào ứng dụng trong thực tế. Ngôn ngữ VHDL được ba công ty Intermetics, IBM và Texas Instruments bắt đầu nghiên cứu phát triển vào tháng 7 năm 1983. Phiên bản đầu tiên được công bố vào tháng 8-1985. Sau đó VHDL được đề xuất để tổ chức IEEE xem xét thành một tiêu chuẩn chung. Năm 1987 đã đưa ra tiêu chuẩn về VHDL (tiêu chuẩn IEEE-1076-1987).

VHDL được phát triển để giải quyết các khó khăn trong việc phát triển, thay đổi và lập tài liệu cho các hệ thống số. Như ta đã biết, một hệ thống số có rất nhiều tài liệu mô tả. Để có thể vận hành bảo trì sửa chữa một hệ thống ta cần tìm hiểu kỹ lưỡng tài liệu đó. Với một ngôn ngữ mô phỏng phần cứng tốt việc xem xét các tài liệu mô tả trở nên dễ dàng hơn vì bộ tài liệu đó có thể được thực thi để mô phỏng hoạt động của hệ thống. Như thế ta có thể xem xét toàn bộ các phần tử của hệ thống hoạt động trong một mô hình thống nhất.

VHDL được phát triển như một ngôn ngữ độc lập không gắn với bất kỳ một phương pháp thiết kế, một bộ mô tả hay công nghệ phần cứng nào. Người thiết kế có thể tự do lựa chọn công nghệ, phương pháp thiết kế trong khi chỉ sử dụng một ngôn ngữ duy nhất. Và khi đem so sánh với các ngôn ngữ mô phỏng phần cứng khác đã kể ra ở trên ta thấy VHDL có một số ưu điểm hơn hẳn các ngôn ngữ khác:

- Thứ nhất là tính công cộng: VHDL được phát triển dưới sự bảo trợ của chính phủ Mỹ và hiện nay là một tiêu chuẩn của IEEE. VHDL được sự hỗ trợ của nhiều nhà sản xuất thiết bị cũng như nhiều nhà cung cấp công cụ thiết kế mô phỏng hệ thống.

- Thứ hai là khả năng hỗ trợ nhiều công nghệ và phương pháp thiết kế. VHDL cho phép thiết kế bằng nhiều phương pháp ví dụ phương pháp thiết kế từ trên xuống, hay từ dưới lên dựa vào các thư viện sẵn có. VHDL cũng hỗ trợ cho nhiều loại công cụ xây dựng mạch như sử dụng công nghệ đồng bộ hay không đồng bộ, sử dụng ma trận lập trình được hay sử dụng mảng ngẫu nhiên.

- Thứ ba là tính độc lập với công nghệ: VHDL hoàn toàn độc lập với công nghệ chế tạo phần cứng. Một mô tả hệ thống dùng VHDL thiết kế ở mức cổng có thể được chuyển thành các bản tổng hợp mạch khác nhau tuỳ thuộc công nghệ chế tạo phần cứng mới ra đời nó có thể được áp dụng ngay cho các hệ thống đã thiết kế.

- Thứ tư là khả năng mô tả mở rộng: VHDL cho phép mô tả hoạt động của phần cứng từ mức hệ thống số cho đến mức cổng. VHDL có khả năng mô tả hoạt động của hệ thống trên nhiều mức nhưng chỉ sử dụng một cú pháp chặt chẽ thống nhất cho mọi mức. Như thế ta có thể mô phỏng một bản thiết kế bao gồm cả các hệ con được mô tả chi tiết.

- Thứ năm là khả năng trao đổi kết quả: Vì VHDL là một tiêu chuẩn được chấp nhận, nên một mô hình VHDL có thể chạy trên mọi bộ mô tả đáp ứng được tiêu chuẩn VHDL. Các kết quả mô tả hệ thống có thể được trao đổi giữa các nhà thiết kế sử dụng công cụ thiết kế khác nhau nhưng cùng tuân theo tiêu chuẩn VHDL. Cũng như một nhóm thiết kế có thể trao đổi mô tả mức cao của các hệ thống con trong một hệ thống lớn (trong đó các hệ con đó được thiết kế độc lập).

- Thứ sáu là khả năng hỗ trợ thiết kế mức lớn và khả năng sử dụng lại các thiết kế: VHDL được phát triển như một ngôn ngữ lập trình bậc cao, vì vậy nó có thể được sử dụng để thiết kế một hệ thống lớn với sự tham gia của một nhóm nhiều người. Bên trong ngôn ngữ VHDL có nhiều tính năng hỗ trợ việc quản lý, thử nghiệm và chia sẻ thiết kế. Và nó cũng cho phép dùng lại các phần đã có sẵn.

2.2. Cấu trúc một mô hình hệ thống mô tả bằng VHDL

Mục đích của phần này là nhằm giới thiệu sơ qua về cấu trúc khung cơ bản của VHDL khi mô tả cho một mô hình thiết kế thực. Thông thường một mô hình VHDL bao gồm ba phần: thực thể (entity), kiến trúc (architecture) và các cấu hình. Đôi khi ta sử dụng các gói (packages) và mô hình kiểm tra hoạt động của hệ thống (testbench).

+ Thực thể (entity)

Đây là nơi chứa các khai báo thực thể (là các port giao tiếp giữa FPGA và các tín hiệu bên ngoài các port này được sử dụng như là lớp vỏ của kiến trúc thiết kế) và có thể bao gồm các tùy chọn “generic” là khai báo chung có thể dễ dàng sửa đổi khi cần.

+ Kiến trúc (architecture)

Phần thứ hai trong mô hình VHDL là khai báo kiến trúc của chương trình. Mỗi một khai báo thực thể đều phải đi kèm với ít nhất một kiến trúc tương ứng. VHDL cho phép tạo ra hơn một kiến trúc cho một thực thể. Phần khai báo kiến trúc có thể bao gồm các khai báo về các tín hiệu bên trong, các phần tử bên trong hệ thống, hay các hàm và thủ tục mô tả hoạt động của hệ thống. Tên của kiến trúc là nhãn được đặt tuỳ theo người xử dụng. Có hai cách mô tả kiến trúc của một phần tử (hoặc hệ thống) đó là mô hình hoạt động (Behaviour) hay mô tả theo mô hình cấu trúc (Structure). Tuy nhiên một hệ thống có thể bao gồm cả mô tả theo mô hình hoạt động và mô tả theo mô hình cấu trúc.

+ Mô tả kiến trúc theo mô hình hoạt động

Mô hình hoạt động mô tả các hoạt động của hệ thống (hệ thống đáp ứng với các tín hiệu vào như thế nào và đưa ra kết quả gì ở đầu ra) dưới dạng các cấu trúc ngôn ngữ lập trình bậc cao. Cấu trúc đó có thể là PROCESS, WAIT, IF, CASE, FOR-LOOP…

+ Mô tả kiến trúc theo mô hình cấu trúc

Mô hình cấu trúc của một phần tử (hoặc hệ thống) có thể bao gồm nhiều cấp cấu trúc bắt đầu từ một cổng logic đơn giản đến xây dựng mô tả cho một hệ thống hoàn thiện. Thực chất của việc mô tả theo mô hình cấu trúc là mô tả các phần tử con bên trong hệ thống và sự kết nối của các phần tử con đó. Như với ví dụ mô tả mô hình cấu trúc một flip-flop RS gồm hai cổng NAND có thể mô tả cổng NAND được định nghĩa tương tự như ví dụ với cổng NOT, sau đó mô tả sơ đồ móc nối các phần tử NAND tạo thành trigơ RS.

+ Cấu trúc process

Process là khối cơ bản của việc mô tả theo hoạt động. Process được xét đến như là một chuỗi các hành động đơn trong suốt quá trình dịch.

Hình 1: Cấu trúc process

S: Mô hình cấu trúc

B: Mô hình hoạt động

S/B: Mô hình kết hợp

Cấu trúc tổng quát

[Process label]

Process [(sensitive_list )]

Process declarative part

Begin

….

End process

Trong đó các phần đặt trong dấu [ ] thì có thể có hoặc không.

- process_label: (nhãn lệnh) là tuỳ thuộc người lập trình đặt tên

- sensitivity_list: Danh sách các yếu tố kích thích hoạt động.

+ Môi trường kiểm tra (testbench)

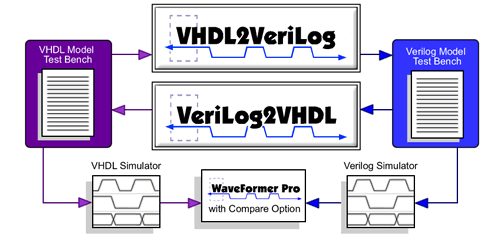

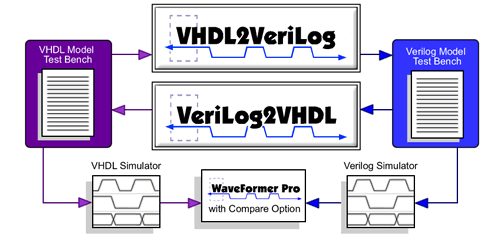

Một trong các nhiệm vụ rất quan trọng là kiểm tra bản mô tả thiết kế. Kiểm tra một mô hình VHDL được thực hiện bằng cách quan sát hoạt động của nó trong khi mô phỏng và các giá trị thu được có thể đem so sánh với yêu cầu thiết kế.

Môi trường kiểm tra có thể hiểu như một mạch kiểm tra ảo. Môi trường kiểm tra sinh ra các tác động lên bản thiết kế và cho phép quan sát hoặc so sánh kết quả hoạt động của bản mô tả thiết kế. Thông thường thì các bản mô tả đều cung cấp chương trình thử. Nhưng ta cũng có thể tự xây dựng chương trình thử (testbench). Mạch thử thực chất là sự kết hợp của tổng hợp nhiều thành phần. Nó gồm ba thành phần. Mô hình VHDL đã qua kiểm tra, nguồn dữ liệu và bộ quan sát. Hoạt động của mô hình VHDL được kích thích bởi các nguồn dữ liệu và kiểm tra tính đúng đắn thông qua bộ quan sát.

Hình 2: Sơ đồ khối của Testbench

Trong đó: DUT: (device under test) mô hình VHDL cần kiểm tra.

Observer: khối quan sát kết quả.

Data source: nguồn dữ liệu (khối tạo ra các tín hiệu kích thích).

3. Giới thiệu khái quát về ngôn ngữ Verilog

Verilog HDL là một trong hai ngôn ngữ mô phỏng phần cứng thông dụng nhất cùng với VHDL được dùng trong thiết kế IC. Verilog HDL cho phép mô phỏng các thiết kế dễ dàng, sửa chữa lỗi, hoặc thực nghiệm bằng những cấu trúc khác nhau. Các thiết kế được mô tả trong Verilog HDL là những kỹ thuật độc lập, dễ thiết kế, dễ tháo gỡ và thường dễ đọc hơn ở dạng biểu đồ, đặc biệt là ở các mạch điện lớn.

Verilog thường được dùng để mô tả thiết kế ở bốn dạng

- Thuật toán (một số lệnh giống ngôn ngữ C như: if, case, for,while…).

- Chuyển đổi thanh ghi (kết nối bằng các biểu thức Boolean).

- Các cổng kết nối (cổng: OR, AND, NOT…).

- Chuyển mạch (BJT, MOSFET).

Ngôn ngữ này cũng chỉ rõ cách thức kết nối, điều khiển vào/ra trong mô phỏng.

Khai báo module

Một module là bản thiết kế chủ yếu tồn tại trong Verilog. Dòng đầu tiên của khai báo module chỉ rõ danh sách tên và port (các đối số). Những dòng kế tiếp chỉ rõ dạng I/O (input, output, hoặc inout) và chiều rộng của mỗi port. Mặc định chiều rộng port là 1 bit.

Sau đó, những biến port phải được khai báo wire, wand, …, reg. Mặc định là wire. Những ngõ vào đặc trưng là wire khi dữ liệu được chốt bean ngoài module. Các ngõ ra là dạng reg nếu những tín hiệu của chúng được chứa trong khối always hoặc initial.

Chỉ thị liên tiếp

Các chỉ định liên tiếp được dùng để gán một giá trị lên trên một wire trong một module. Đó là các chỉ định thông thường bên ngoài khối always hoặc khối initial. Các chỉ định liên tiếp được thực hiện với một lệnh gán (assign) rõ ràng hoặc bằng sự chỉ định một giá trị đến một wire trong lúc khai báo. Chú ý rằng, các lệnh chỉ định liên tiếp thì tồn tại và được chạy liên tục trong suốt quá trình mô phỏng. Thứ tự các lệnh gán không quan trọng. Mọi thay đổi bên phải của bất cứ ngõ vào sẽ lập tức thay đổi bên trái của các ngõ ra.

Module instantiations

Những khai báo module là những khuôn mẫu mà nó được tạo nên từ các đối tượng thực tế (instantiation). Các module đơn cử bên trong các module khác, và mỗi dẫn chứng tạo một đối tượng độc nhất từ khuôn mẫu. Ngoại trừ đó là module mức trên là những dẫn chứng từ chính chúng. Các port của module ví dụ phải thỏa những định nghĩa trong khuôn mẫu. Đây là mặt lý thuyết: bằng tên, sử dụng dấu chấm (.) ”.tên port khuôn mẫu (tên của wire kết nối đến port)”. Bằng vị trí, đặt những port ở những vị trí giống nhau trong danh sách port của cả khuôn mẫu lẫn instance.

BEHAVIORAL

Verilog có 4 mức khuôn mẫu:

- Chuyển mạch.

- Cổng.

- Mức tràn dữ liệu.

- Hành vi hoặc thủ tục được đề cập ở bên dưới.

Các lệnh thủ tục Verilog được dùng tạo một mẫu thiết kế ở mức cao hơn. Chúng chỉ ra những cách thức mạnh của vệc làm ra những thiết kế phức tạp. Tuy nhiên, những thay đổi nhỏ n phương pháp mã hóa có thể gây ra biến đổi lớn trong phần cứng. Các lệnh thủ tục chỉ có thể được dùng trong những thủ tục.

Những chỉ định theo thủ tục:

Là những chỉ định dùng trong phạm vi thủ tục Verilog (khối always và initial). Chỉ biến reg và integers (hoặc chọn đơn bit/ nhóm bit của chúng hoặc kết nối thông tin) có thể được đặt bên trái dấu ‘=’ trong thủ tục. Bên phải của chỉ định là một biểu thức mà có thể dùng bất cứ dạng toán tử nào.

Delay trong chỉ định:

Trong chỉ định trễ ∆t là khoảng thời gian trải qua trước khi một lệnh được thực thi và bên trái lệnh gán được tạo ra. Với nhiều chỉ định trễ (intra-assignment delay), bên phải được định giá trị trực tiếp nhưng có một delay của ∆t trước khi kết quả được đặt bên trái lệnh gán. Nếu thêm một quá trình thay đổi nữa cạnh bên phải tín hiệu trong khoảng thơi gian ∆t, thì không cho kết quả ở ngõ ra. Delay không được hỗ trợ bởi các công cụ.

Cấu trúc chương trình dùng ngôn ngữ Verilog

// Khai báo module

Module tên chương trình (tên biến I/O); // tên chương trình trùng tên file.v.

Input [msb:lsb] biến;

Output [msb:lsb] biến;

Reg [msb:lsb] biến reg;

Wire [msb: lsb] biến wire;

// Khai báo khối always, hoặc khối initial.

… các lệnh …

Nguồn: tieuluan

Bạn Có Đam Mê Với Vi Mạch hay Nhúng - Bạn Muốn Trau Dồi Thêm Kĩ Năng

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn

Bạn Chưa Biết Phương Thức Nào Nhanh Chóng Để Đạt Được Chúng

Hãy Để Chúng Tôi Hỗ Trợ Cho Bạn. SEMICON

Hotline: 0972.800.931 - 0938.838.404 (Mr Long)