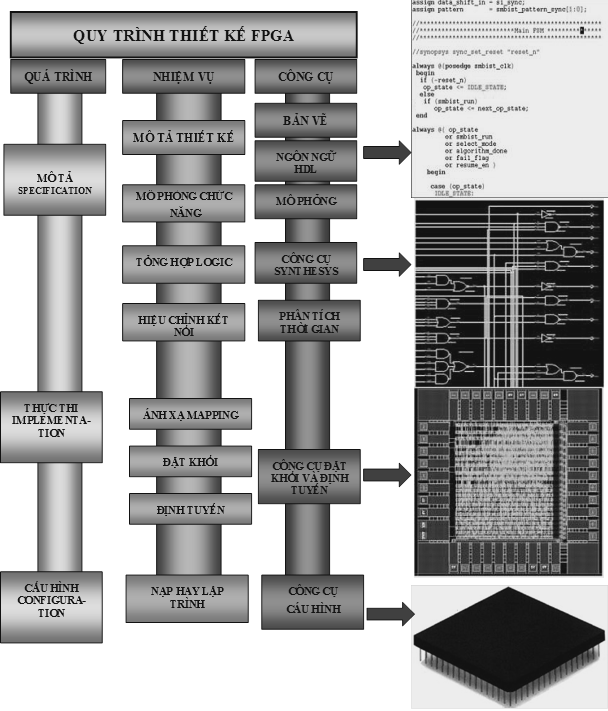

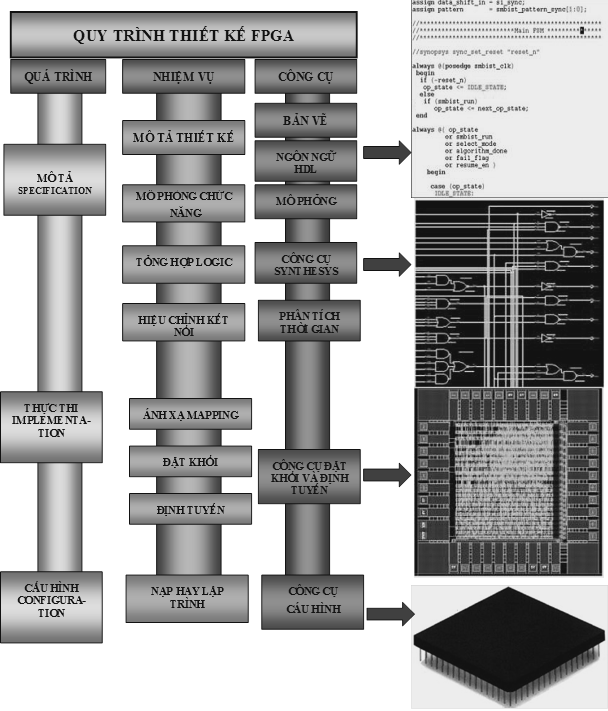

- Khi xây dựng một chip khả trình (FPGA) với ý nghĩa dành cho một ứng dụng riêng biệt. Chính vì xuất phát từ mỗi ứng dụng trong thực tiễn cuộc sống, ta sẽ phải đặt ra yêu cầu thiết kế IC thực hiện tối ưu nhất những ứng dụng đó. Bước đầu tiên của quy trình thiết kế này có nhiệm vụ tiếp nhận các yêu cầu của thiết kế và xây dựng nên kiến trúc tổng quát của thiết kế.

- Mô tả thiết kế(Design Specification)

- Trong bước này, từ những yêu cầu của thiết kế và dựa trên khả năng của công nghệ hiện có, người thiết kế kiến trúc sẽ xây dựng nên toàn bộ kiến trúc tổng quan cho thiết kế. Nghĩa là trong bước này người thiết kế kiến trúc phải mô tả được những vấn đề sau:

- Thiết kế có những khối nào?

- Mỗi khối có chức năng gì?

- Hoạt động của thiết kế và của mỗi khối ra sao ?

- Phân tích các kỹ thuật sử dụng trong thiết kế và các công cụ, phần mềm hỗ trợ thiết kế.

- Mô phỏng chức năng (Function simulation).

Sau khi mô tả thiết kế, người thiết kế cần mô phỏng tổng thể thiết kế về mặt chức năng để kiểm tra thiết kế có hoạt động đúng với các chức năng yêu cầu.

- Tổng hợp logic (Logic Synthesis).

+ Tổng hợp logic là quá trình tổng hợp các mô tả thiết kế thành sơ đồ bố trí mạch (netlist). Quá trình chia thành 2 bước: chuyển đổi các mã RTL, mã HDL thành mô tả dưới dạng các biểu thức đại số Boolean và dựa trên các biểu thức này kết hợp với thư viện tế bào chuẩn sẵn có để tổng hợp nên một thiết kế tối ưu.

- Hiệu chỉnh các kết nối (Datapath Schematic).

+ Nhập netlist và các ràng buộc về thời gian vào một công cụ phân tích thời gian (timing analysic). Công cụ phân tích này sẽ tách rời tất cả các kết nối của thiết kế, tính thời gian trễ của các kết nối dựa trên các ràng buộc. Dựa trên kết quả phân tích (report) của công cụ phân tích, xác định các kết nối không thỏa mãn về thời gian. Tùy theo nguyên nhân dẫn đến không thỏa mãn mà ta có thể viết lại mã và tiến hành lại tổng hợp logic hoặc hiệu chỉnh lại các ràng buộc.

3.1.2 Thực thi (Implementation).

+ Ta đã có sơ đồ bố trí netlist mô tả tổng thể thiết kế tại mức cổng (chỉ gồm các cổng logic cơ bản và các mạch logic khác như: MUX). Quá trình này sẽ đặt sơ đồ netlist này lên chip, gọi là quá trình thực thi (Device Implementation).

++Quá trình gồm các bước:

- Ánh xạ (mapping hay còn gọi fitting - ăn khớp) : chuẩn bị dữ liệu đầu vào, xác định kích thước các khối. Các khối này sẽ phải phù hợp với cấu trúc của 1 tế bào cơ bản của FPGA. (gồm nhiều cổng logic) và đặt chúng vào các vị trí tối ưu cho việc chạy dây.

![[IMG]](https://lh4.googleusercontent.com/-Xg4K5791Ink/VaXaKjJBRtI/AAAAAAAACRQ/znwPUF9bXac/w722-h542-no/3.png)

- Đặt khối và định tuyến (Place & Route):

+ Đặt khối: đặt các khối ánh xạ vào các tế bào (cell) ở vị trí tối ưu cho việc chạy dây.

![[IMG]](https://lh4.googleusercontent.com/-RRh6C0ElDkI/VaXaLcS5p2I/AAAAAAAACRk/4gc-TbZ2MyY/w722-h542-no/4.png)

+Định tuyến: Bước này thực hiện việc nối dây các tế bào.

![[IMG]](https://lh6.googleusercontent.com/-PepcIUvFVp8/VaXaLhWgZiI/AAAAAAAACRg/v2TPtlp7htg/w893-h671-no/6.png)

Để thực hiện việc này, chúng ta cần có các thông tin sau:

- Các thông tin vật lý về thư viện tế bào, ví dụ kích thước tế bào, các điểm để kết nối, định thời, các trở ngại trong khi đi dây.

- Một netlist được tổng hợp sẽ chỉ ra chi tiết các instance và mối quan hệ kết nối bao gồm cả các đường dẫn bị hạn chế trong thiết kế.

- Tất cả các yêu cầu của tiến trình cho các lớp kết nối, bao gồm các luật thiết kế cho các lớp chạy dây, trở kháng và điện dung, tiêu thụ năng lượng, các luật về sự dẫn điện trong mỗi lớp.

3.1.3. Quá trình Nạp (download) và lập trình (program).

- Sau quá trình thực hiện, thiết kế cần được nạp vào FPGA dưới dạng dòng bit (bit stream).

- Quá trình nạp thiết kế (download) vào FPGA thường nạp vào bộ nhớ bay hơi, ví dụ như SRAM. Thông tin cấu hình sẽ được nạp vào bộ nhớ. Dòng bit được truyền lúc này sẽ mang thông tin định nghĩa các khối logic cũng như kết nối của thiết kế. Tuy nhiên, lưu ý rằng, SRAM sẽ mất dữ liệu khi mất nguồn nên thiết kế sẽ không lưu được đến phiên làm việc kế tiếp.

- Lập trình (program) là thuật ngữ để mô tả quá trình nạp chương trình cho các bộ nhớ không bay hơi, ví dụ như PROM. Như vậy, thông tin cấu hình vẫn sẽ được lưu trữ khi mất nguồn.

Bạn có đam mê ngành thiết kế vi mạch và bạn muốn có mức lương 1000 usd cùng lúc bạn

đang muốn tìm một Trung tâm để học vậy hãy đến với ngành vi mạch tại SEMICON